UVM Doğrulaması

- FİGES AŞ

- MATLAB&Simulink

- Uygulama Alanları

- FPGA, ASIC, SoC Geliştirme

- UVM Doğrulaması

UVM Doğrulaması Nedir?

Evrensel Doğrulama Metodolojisi (UVM) doğrulaması, ASIC ve FPGA projelerinde kullanılan standartlaştırılmış bir tasarım doğrulama şeklidir. UVM, bir standart kuruluşu olan Accellera tarafından kolaylaştırıldı ve elektronik tasarım otomasyon endüstrisindeki önde gelen şirketler tarafından geliştirilen ASIC doğrulama metodolojilerine dayanıyordu.

UVM doğrulamasının temel amacı, yeniden kullanılabilir doğrulama bileşenlerinin kullanımı yoluyla tasarım doğrulama verimliliğini artırmaktır. Bununla birlikte, UVM doğrulama bileşenlerinin manuel olarak oluşturulması ve hatalarının ayıklanması, özellikle yeni algoritmik içerik için yine de önemli miktarda çaba gerektirebilir ve UVM’nin karmaşıklığı, tasarım ekipleri tarafından benimsenmesinin önünde bir engel olabilir.

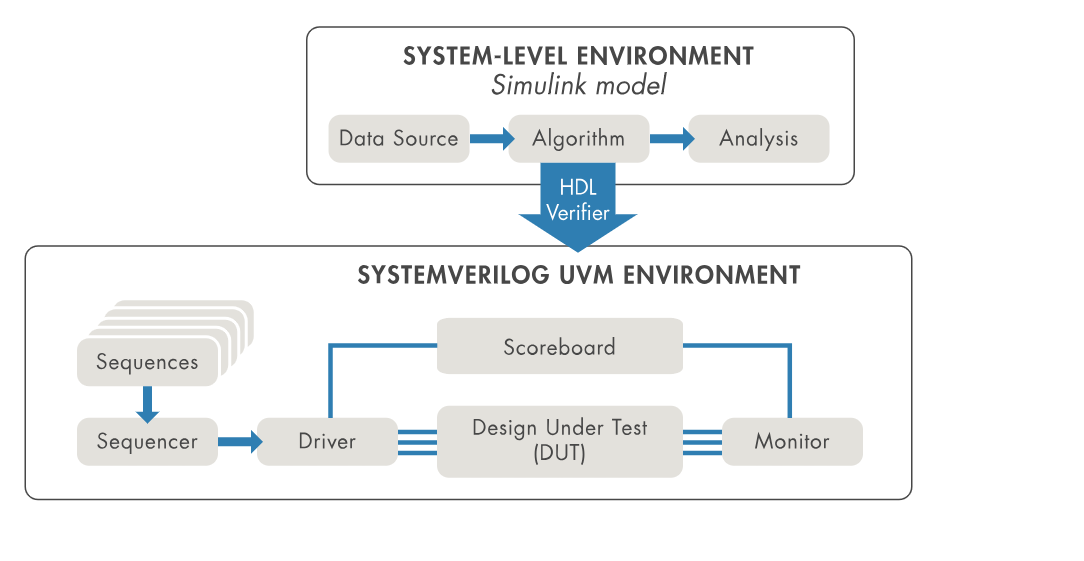

ASIC ve FPGA tasarım projeleri için geliştirilen birçok algoritma MATLAB® kodu veya Simulink® modelleri olarak başladığından, tasarım ekipleri doğrudan MATLAB veya Simulink kaynağından UVM doğrulama bileşenleri üreterek ASIC testbench geliştirme işlemlerini azaltabilir. HDL Verifier™, MATLAB kodundan veya Simulink modellerinden SystemVerilog DPI bileşenlerini otomatik olarak oluşturabilir. Bu bileşenler, bir UVM doğrulama çetelesinde altın referans denetleyici modelleri olarak, karma sinyal simülasyonunda davranışsal dijital veya analog bileşen modelleri olarak veya bir UVM doğrulama uyarıcısı olarak hizmet eden diziler olarak kullanılabilir.

HDL Doğrulayıcı ayrıca doğrudan Simulink modellerinden eksiksiz UVM doğrulama ortamları da oluşturabilir. HDL Verifier, test modellerinden SystemVerilog UVM dizisi, sürücü, monitör ve puan tablosu bileşenleri oluşturur. Ayrıca test edilen davranışsal tasarım (DUT) için SystemVerilog dosyaları üretir. Davranışsal DUT daha sonra manuel olarak kodlanan RTL veya HDL Coder kullanılarak oluşturulan RTL ile değiştirilebilir. Oluşturulan UVM doğrulama ortamları, Siemens® ModelSim® veya Questa®, Cadence® Xcelium™ veya Synopsys® VCS® ile kullanılabilir.

UVM doğrulamasının bazı uygulamalarında, MATLAB veya Simulink’ten tam UVM ortamları yerine bireysel UVM bileşenlerini oluşturmayı tercih edebilirsiniz. MATLAB’den bireysel UVM bileşenleri oluşturmak için tahmin edici, dizi veya skor tablosu bileşenleri için UVM şablonlarını kullanabilirsiniz. Benzer şekilde, Simulink alt sistemlerinden de diziler, tahmin ediciler veya skor tabloları için UVM bileşenleri oluşturabilirsiniz.

UVM Framework’ü kullanarak UVM doğrulama ortamları geliştiriyorsanız, ASIC Testbench’i kullanarak bir UVM Framework İş Akışı içinde SystemVerilog DPI bileşenleri oluşturabilirsiniz.

Bir Simulink modelinden bir UVM test bench oluşturarak UVM doğrulaması gerçekleştirin.

Ek bilgi için bkz. HDL Doğrulayıcı.

Örnekler ve Nasıl Yapılır?

UVM Doğrulama Ortamları Oluşturma

• UVM Bileşen Üretimine Genel Bakış – Belgeleme

• Simulink’ten Parametreli UVM Test Bench Oluşturun – Örnek

• UVM Test bench için Dizilere Rastgele Kısıtlamalar Ekleme – Örnek

• UVM Test bench Davranışsal DUT’yi AXI Tabanlı RTL DUT ile Değiştirin – Örnek

• UVM Test bench Scoreboard Parametrelerini Değiştirme – Örnek

• Sürücü ve Monitörü UVM Test bench’e Dahil Etme – Örnek

–SystemVerilog DPI’yi UVM Framework İş Akışına Entegre Etme – Örnek

MATLAB ile SystemVerilog DPI-C Bileşenleri Oluşturma

• HDL Doğrulayıcı Kullanarak MATLAB’den DPI-C Modelleri Oluşturma (5:19) – Video

• MATLAB ile SystemVerilog DPI Bileşeni Oluşturmaya Başlarken – Örnek

• Şablonları Kullanarak SystemVerilog DPI ve UVM Bileşenleri Oluşturma – Örnek

• 5G Kablosuz Uygulamalarını SystemVerilog DPI Kullanarak Doğrulayın – Örnek

• UART Alıcısı için FIFO Arayüzü DPI Bileşeni Oluşturun – Örnek

• SystemVerilog DPI Bileşeninde Değişken Boyutlu Vektör Kullanın – Örnek

UVM Doğrulaması için Simulink ile SystemVerilog DPI-C Bileşenleri Oluşturma

• Simulink’ten SystemVerilog DPI Bileşeni Oluşturmaya Başlarken – Örnek

UVM Testbench’te Davranışsal DUT’yi RTL DUT ile Değiştirme – Örnek

• HDL Doğrulayıcı SystemVerilog DPI Test Noktası Ekleme (3:34) – Video

• Oluşturulan SystemVerilog Kodunu Özelleştirmeye Başlarken – Örnek

• QAM Alıcı-Verici Modeli için HDL Test Tezgahı Oluşturma – Örnek

UVM Testbench’teki Skor Tablosunun Parametrelerini ve Kapsam Hedeflerini Değiştirme – Örnek