Verilog TestBench’i

- FİGES AŞ

- MATLAB&Simulink

- Probleminizi Nasıl Çözeceğinizi Keşfedin

- Verilog TestBench’i

Verilog TestBench Nedir?

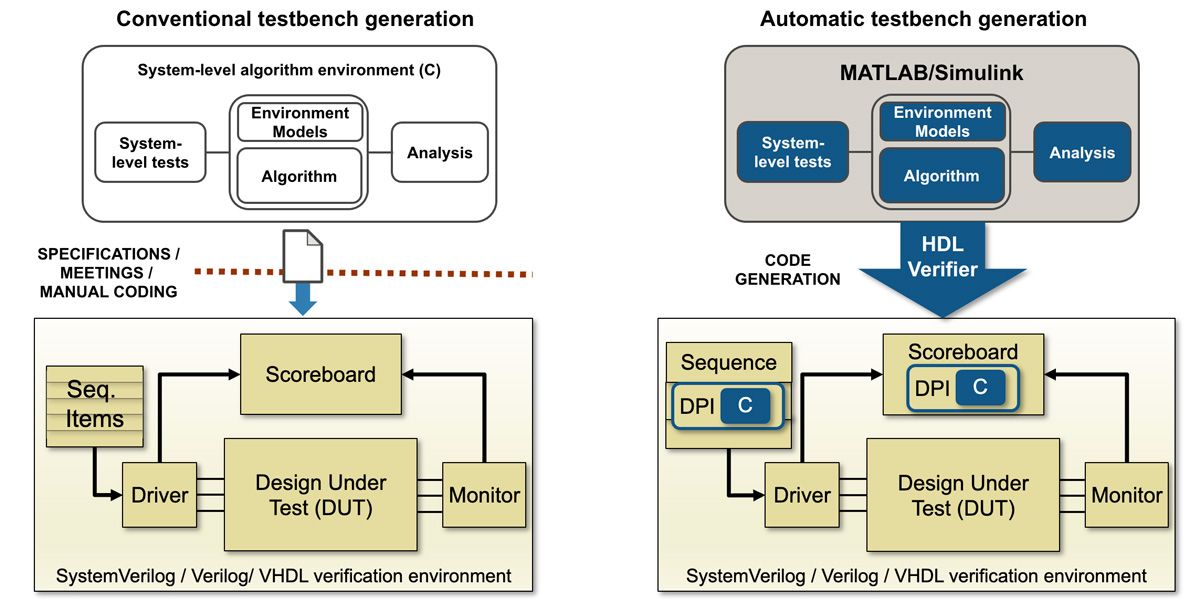

Geleneksel bir Verilog® testbench, bir mantık tasarımına yönelik girdiyi tanımlayan ve tasarımın çıktılarının spesifikasyonla uyumlu olup olmadığını kontrol eden bir kod modülüdür. Birçok mühendis, MATLAB® ve Simulink® yazılımlarını spesifikasyon modellerine yönelik sistem testbench’leri oluşturmak için kullanır çünkü bu yazılımlar, algoritmaları tanımlamak için verimli ve kompakt bir notasyon sunmanın yanı sıra, algoritma davranışlarını incelemek için görselleştirme araçları sağlar. Daha sonra bu sistem testbench’lerine dayalı olarak Verilog testbench’leri geliştirirler.

MATLAB veya Simulink kullanıcılarının, HDL algoritma gerçekleştirmelerinin doğru olduğunu manuel olarak Verilog testbench’leri kodlamadan doğrulamak için birkaç seçeneği vardır.

Verilog Testbench’lerine Alternatif Olarak HDL Cosimulation Kullanımı

Bir Verilog testbench yazmak yerine, tasarımınızı test etmek için bir MATLAB veya Simulink testbench’i ile bir HDL simülatörünü birleştirebilirsiniz. HDL Verifier™, bu cosimulation sürecini otomatikleştirir. MATLAB veya Simulink testbench’i, HDL simülatöründen gelen çıktı değerlerini bir doğruluk modeliyle karşılaştırır ve “uyuşmazlıklar” raporlar.

Verilog Testbench’lerine Alternatif Olarak FPGA-in-the-Loop Testi Kullanımı

Bir MATLAB veya Simulink testbench’ini, FPGA-in-the-loop simülasyonu yoluyla bir AMD®, Intel® veya Microchip® FPGA geliştirme kartına programlanmış bir tasarım (DUT) ile birlikte kullanabilirsiniz. HDL Verifier, FPGA üreticisi araçlarıyla HDL’yi derlemek, bir programlama dosyası oluşturmak, bu dosyayı geliştirme kartına yüklemek ve MATLAB veya Simulink oturumu ile kart arasındaki iletişimi etkinleştirmek için kullanılabilir. FPGA-in-the-loop yöntemiyle, bir Verilog testbench oluşturmanıza gerek yoktur çünkü bu işlevi MATLAB veya Simulink yerine getirir.

Verilog Testbench’lerine Alternatif Olarak SystemVerilog DPI Testbench Üretimi Kullanımı

Verilog testbench kullanmaya alternatif bir yöntem, kodu HDL simülatörlerine dışa aktarmaya dayanır. Testbench geliştirmek için kullanılan Verilog’un bir uzantısı olan SystemVerilog, tüm popüler HDL simülatörleri tarafından desteklenir. SystemVerilog Direct Programming Interface (DPI) ile, Synopsys® VCS®, Cadence® Xcelium™ ve Siemens® ModelSim® veya Questa® gibi simülatörlere C/C++ kodunu entegre edebilirsiniz. HDL Verifier, MATLAB Coder™ veya Simulink Coder™ ile birlikte kullanılarak, ürünleri doğrulamak için SystemVerilog DPI testbench’leri oluşturmanıza olanak tanır.

DPI Üretimine Erişim için

MATLAB kodu veya Simulink alt sistemleri için DPI Üretimine erişmek amacıyla, öncelikle ASIC Testbench for HDL Verifier eklentisini indirip yükleyin.

HDL Verifier, iki farklı şekilde SystemVerilog DPI testbench’leri üretebilir:

- Bileşen testbench’i: Bir Simulink alt sisteminden DPI bileşeni olarak kullanılmak üzere bir C bileşeni oluşturursanız, bir SystemVerilog testbench’i oluşturabilirsiniz. Bu testbench, oluşturulan DPI bileşenini Simulink modelinizden alınan veri vektörlerine karşı doğrular. (Bkz. SystemVerilog DPI Bileşeni Üretme.)

- HDL kodu testbench’i: Eğer HDL Coder™ kullanarak bir Simulink alt sisteminden HDL kodu oluşturursanız, bir SystemVerilog testbench’i oluşturabilirsiniz. Bu testbench, HDL uygulamasının çıktısını Simulink modelinin sonuçlarıyla karşılaştırır. (Bkz. SystemVerilog DPI Testbench Kullanarak HDL Tasarımını Doğrulama.)

Verilog Testbench’lerine Alternatif Olarak UVM Bileşen veya Ortam Üretiminin Kullanılması

Universal Verification Methodology (UVM), FPGA ve ASIC tasarım projelerinde kullanılan standartlaştırılmış bir tasarım doğrulama yöntemi sağlar. UVM doğrulamasının temel amacı, yeniden kullanılabilir doğrulama bileşenleri kullanarak tasarım doğrulama verimliliğini artırmaktır. ASIC Testbench ile, bir Simulink modelinden UVM test bileşenleri ve davranışsal bir test edilen tasarım (DUT) oluşturabilirsiniz. Oluşturulan bileşenleri iki şekilde kullanabilirsiniz:

- Bir testbench ve davranışsal bir DUT içeren bir UVM üst modeli oluşturun. Oluşturulan UVM üst modülünü bir test ortamı olarak kullanın ve oluşturulan davranışsal DUT’yi kendi simülasyon modelinizle değiştirin.

- UVM test bileşenlerini oluşturun ve mevcut UVM ortamınıza entegre edin.

HDL Coder‘ı kullanarak HDL kodu oluşturduğunuzda, bir alt sistem için Verilog testbench oluşturabilirsiniz. HDL Coder, giriş vektörlerini ve DUT için beklenen çıkış verilerini yakalamak amacıyla bir Simulink simülasyonu çalıştırarak Verilog testbench oluşturur. HDL Coder, MATLAB veya Simulink simülasyonunuzdan DUT uyaranlarını ve referans verilerini .dat veri dosyalarına kaydeder.

HDL simülasyonu sırasında, HDL testbench bu kaydedilen uyaranları .dat dosyalarından okur. Testbench, gerçek DUT çıktısını beklenen çıkışla karşılaştırır.

Örnekler ve Nasıl Yapılır?

HDL Cosimulation

FPGA-in-the-Loop Simülasyonu

SystemVerilog DPI Testbench

UVM Bileşenleri ve Ortamları

- UVM Bileşen Üretimine Genel Bakış – Dokümantasyon

- Simulink’ten Parametreli UVM Testbench Üretme – Örnek

- UVM Testbench’teki Davranışsal DUT’u AXI Tabanlı RTL DUT ile Değiştirme – Örnek

- UVM Testbench’te Sekanslara Rastgele Kısıtlar Ekleme – Örnek

- UVM Testbench’te Skor Tablosu Parametrelerini Değiştirme – Örnek

- UVM Testbench’te Skor Tablosu Parametrelerini ve Kapsama Hedeflerini Değiştirme – Örnek