FPGA Görüntü İşleme

- FİGES AŞ

- MATLAB&Simulink

- Probleminizi Nasıl Çözeceğinizi Keşfedin

- FPGA Görüntü İşleme

FPGA Görüntü İşleme Nedir?

FPGA ve ASIC donanımı için video ve görüntü işleme algoritmaları tasarlayın ve uygulayın

FPGA görüntü işleme, düşük gecikme süresi ve yüksek verimli hesaplama sağlayan özel donanım kullanarak yoğun işlem gerektiren video ve görüntü işleme gerçekleştirir. Bu teknikler genellikle, yazılımda veya derin öğrenme ağında daha fazla işleme için gelen bir video akışının önceden işlenmesini içerir.

FPGA görüntü işleme algoritmalarınız için uygulama seçeneklerini keşfetmek üzere MATLAB® ve Simulink®’i birlikte kullanabilirsiniz. Seçenekler arasında donanım ve yazılım arasında bölümleme, donanım mikro mimarisi ekleme ve sabit nokta niceleme yer alır. Her adımda, yeni sürümü simüle edebilir ve sonuçları referans algoritmayla karşılaştırabilirsiniz.

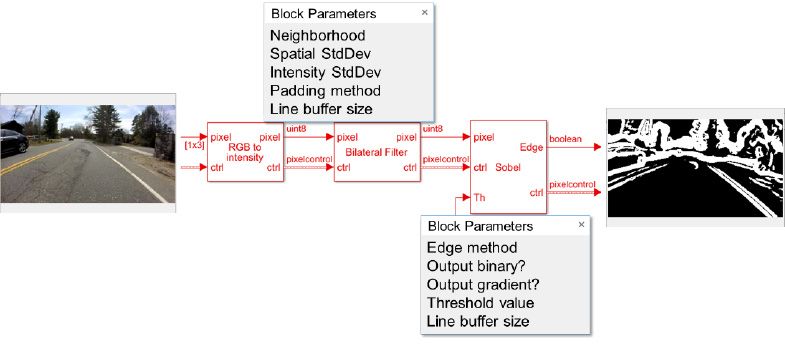

Donanım açısından kanıtlanmış FPGA görüntü işleme blokları, örnek tasarımlar ve Vision HDL Toolbox™ yardımcı programları ile hızlı bir başlangıç yapın. HDL kodu yazmak zorunda kalmadan FPGA görüntü işleme algoritmalarınızı tasarlamak, keşfetmek ve simüle etmek için bu blokları kullanabilirsiniz.

Donanım açısından kanıtlanmış FPGA görüntü işleme blokları şunları içerir:

• Kenar ve köşe algılama

• İkili (Bilateral) ve medyan filtreleme

• Renk alanı (Renk uzayı), kroma yeniden örnekleme, gama düzeltme ve kuşbakışı görünüm gibi dönüşümler

• Morfolojik kapanma, açılma, genişleme ve erozyon

• Satır arabelleği (Line Buffer), piksel akışı hizalayıcı ve ROI seçici gibi yardımcı programlar

Şekil 1. Bir video akışını ön işlemek için donanım tarafından kanıtlanmış ve yapılandırılabilir FPGA görüntü işleme bloklarının kullanılması.

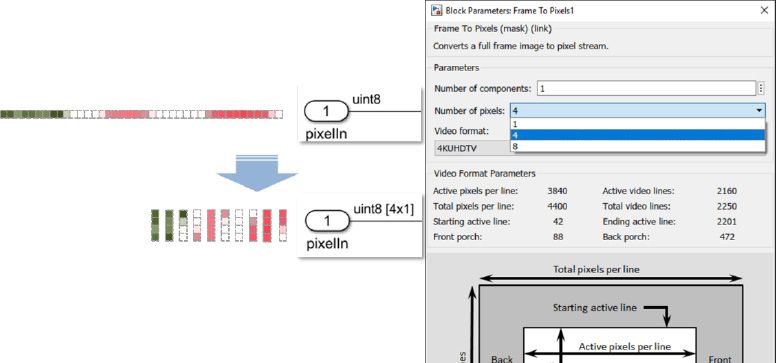

FPGA görüntü işleme, bir piksel akışı üzerinde çalıştığından, bu blokların birçoğu doğası gereği birden çok pikselin veya birden çok bileşenin paralel olarak işlenmesini destekler. Bu, farklı paralellik düzeylerinin faydalarını ve maliyetlerini hızla keşfetmenizi sağlar.

Şekil 2. Piksel ve bileşen işleme için farklı paralellik düzeyleriyle ilişkili ödünleşimleri keşfedin.

FPGA görüntü işleme algoritmanızın gerekli işlevsellik ve performansı karşıladığını doğrulamak için yeterli sayıda simülasyon çalıştırdıktan sonra, deployment için sentezlenebilir VHDL veya Verilog oluşturmak üzere HDL Coder™‘ı kullanabilirsiniz.

Örnekler ve Nasıl Yapılır?

Videolar

- Gömülü Cihazlarda Derin Öğrenme Dağıtımı – FPGA’lar Mantıklı Olduğunda (20:58) – Video

- FPGA Programlama için Sabit Nokta Kolaylaştı (30:45) – Video

- Vision HDL Toolbox’ta Saat Başına Çoklu Piksel İşleme (3:02) – Video

Software Reference

- Frame To Pixels – Documentation

- Pixels To Frame – Documentation

- Hardware-ready image and video processing algorithms – Documentation

- Prototype Vision Algorithms on Zynq-Based Hardware – Documentation

Yazılım Referansı

- Kareden Piksele – Dokümantasyon

- Pixels To Frame – Dokümantasyon

- Donanıma hazır görüntü ve video işleme algoritmaları – Dokümantasyon

- Zynq Tabanlı Donanım Üzerinde Prototip Görüntü Algoritmaları – Dokümantasyon

See also: HDL Coder™, HDL Verifier™

Ayrıca bakınız: HDL Coder™, HDL Verifier™